Fonctions intrinsèques pour sécuriser le calcul CMOS: variabilité, modélisation et sensibilité au bruit (projet électrique / informatique)

->

ABSTRAIT

Une prémisse de base derrière le calcul sécurisé moderne est la demande de primitives cryptographiques légères, comme l’identifiant ou le générateur de clés. Du point de vue des circuits, le développement de modules cryptographiques a également été motivé par la évolutivité agressive de la technologie complémentaire métal-oxyde-semi-conducteur (CMOS). Tout en progressant dans le régime nanométrique, une caractéristique importante de la conception CMOS actuelle est la nature aléatoire de la variabilité du processus, qui limite la conception nominale du circuit. Avec la mise à l’échelle continue de la technologie CMOS, au lieu d’atténuer la variabilité physique, tirer parti de ces propriétés devient un moyen prometteur. L’un des produits célèbres adhérant à cette philosophie de l’épée à double tranchant est les fonctions physiquement inclonables (PUF), qui extraient les clés secrètes des variabilités de fabrication incontrôlables sur les circuits intégrés (CI). Cependant, étant donné que les PUF tirent parti des variations microscopiques des processus, de nombreux problèmes spécialisés, notamment la variabilité, les attaques de modélisation et la sensibilité au bruit, doivent être pris en compte et résolus.

Dans cette thèse, nous présentons nos travaux récents sur le calcul sécurisé basé sur PUF sous trois aspects: la variabilité, la modélisation et la sensibilité au bruit, qui sont considérés comme les fondements de notre étude. De plus, nous avons constaté que les trois facteurs se coordonnent les uns aux autres dans notre étude, par exemple, la technique de modélisation peut être utilisée pour améliorer la fiabilité insatisfaite causée par la sensibilité au bruit, la quantification de la variabilité peut éliminer efficacement l’impact du bruit, et la modélisation peut aider avec caractériser la variabilité physique avec précision.

FONCTIONS PHYSIQUES NON CLONABLES FIABLES UTILISANT UNE TENSION DE RÉTENTION DE DONNÉES DE CELLULES SRAM

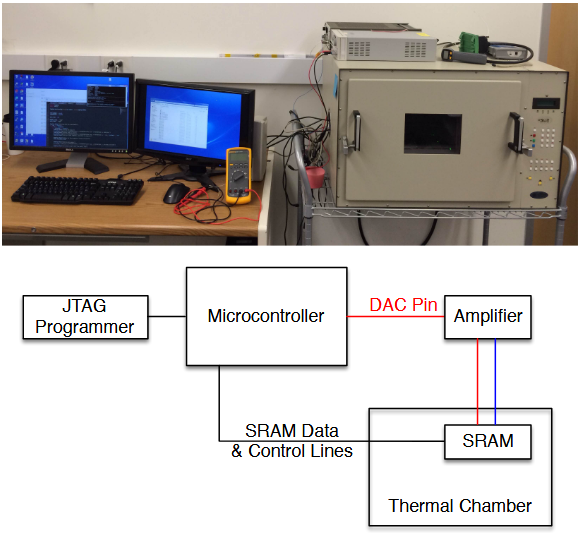

La plate-forme cible pour les empreintes digitales DRV est un bloc SRAM intégré avec une tension d’alimentation réglable, comme cela est parfois utilisé pour compenser la variation.Pour simplifier les expériences, notre plate-forme imite cette configuration à l’aide d’une puce SRAM dédiée et d’un microcontrôleur séparé. La figure 2.2 présente un aperçu de notre système expérimental. Les tensions d’alimentation SRAM sont générées à l’aide des sorties analogiques d’un microcontrôleur Texas Instruments MSP430 F2618, et ce même microcontrôleur orchestre également la synchronisation des changements de tension d’alimentation (selon Proc.1). Un amplificateur opérationnel configuré comme un suiveur de tension suit la tension de sortie analogique du microcontrôleur et alimente la SRAM à la même tension; l’ampli-op est utilisé parce que la sortie analogique du microcontrôleur ne peut pas fournir suffisamment de courant pour alimenter directement la SRAM.

Figure 2.7: Erreur de prédiction DRV pour le modèle de réseau de neurones artificiels et le modèle de régression linéaire

Dans les deux cas, l’erreur est déterminée par comparaison avec les résultats simulés par SPICE. La figure 2.7 présente l’erreur de prédiction de ces modèles. Le modèle de réseau neuronal produit des erreurs de prédiction plus petites que le modèle de régression linéaire. La moyenne μ et l’écart type σ de l’erreur de prédiction pour le modèle de réseau neuronal sont respectivement de – 0,01 mV et 0,35 mV, tandis que ceux du modèle de régression linéaire sont de 0,041 mV et 0,9 mV.

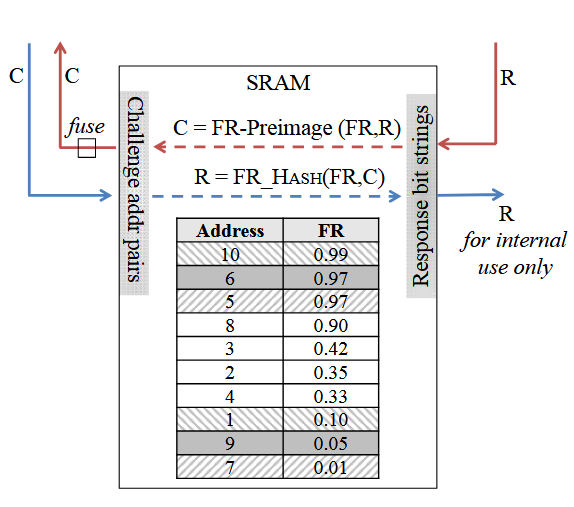

Figure 2.9: Exemple de hachage DRV

Selon l’affectation DRV illustrée D, et en laissant le défi C être (〈1,10, 〈6,9〉, 〈7, 5〉), la procédure DH (D, C) produit la réponse R = (1,0,1) . De même, la procédure DH-Preimage (D, R), compte tenu de cette réponse R, produirait en sortie le même défi C.

Une démonstration du hachage basé sur DRV est donnée à la Fig.2.9. Selon l’affectation DRV illustrée D, la procédure DH hache le défi C = (〈1, 10〉, 〈6, 9〉, 〈7, 5〉) à la réponse R = (1,0,1): le premier bit de réponse est 1 car l’adresse 10 a un DRV plus élevé que l’adresse 1, le deuxième bit de réponse est 0 parce que l’adresse 6 a un DRV plus élevé que l’adresse 9 et le troisième bit de réponse est 1 parce que l’adresse 5 a un DRV plus élevé que l’adresse 7.

CONCEPTION FIABLE DE PUF UTILISANT DES MOTIFS DE DÉFAILLANCE À PARTIR D’UN RÉSEAU ÉLECTRIQUE À CONTRÔLE TEMPOREL

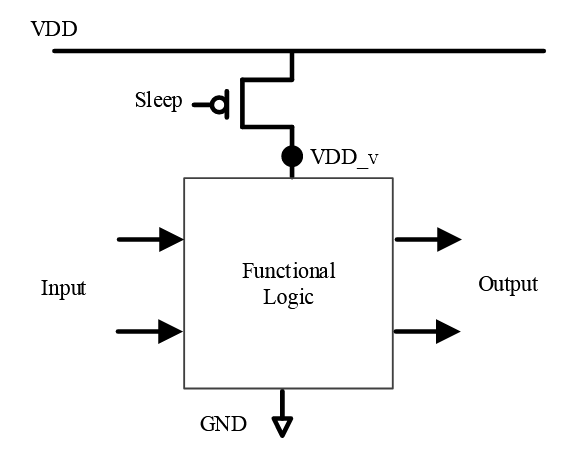

Figure 3.1: Schéma de la coupure d’alimentation à l’aide d’un commutateur d’en-tête

Un transistor PMOS est utilisé entre le nœud d’alimentation (VDD) et le nœud d’alimentation virtuel (VDDV) qui alimente directement le bloc. Un signal de veille active et désactive la connexion entre VDD et VDDV.

Le découpage de puissance est une technique d’économie d’énergie pour les systèmes embarqués dans lesquels l’alimentation est effectivement coupée pour les parties inactives de la puce. Le découpage de puissance est courant dans les systèmes embarqués modernes, y compris les FPGA Xilinx 7 et les processeurs ARM Cortex-M. Un exemple de schéma de logique à découpage de puissance est illustré à la Fig.3.1; un transistor PMOS est inséré entre la tension d’alimentation normale (VDD) et une tension d’alimentation virtuelle (VDDV) qui alimente directement la logique.

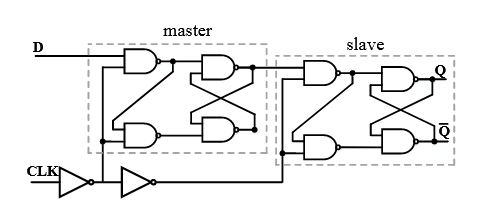

Figure 3.2: Schéma d’une bascule D maître-esclave déclenchée par front positif

Q et ̄ Q sont les nœuds d’état complémentaires qui stockent une valeur de bit unique entre les portes NAND à couplage croisé. La valeur d’entrée D est stockée dans le verrou principal lorsque CLK augmente. Presque simultanément, le verrou esclave s’ouvre pour permettre au signal stocké du maître de se propager à travers l’esclave vers la sortie.

Notre travail emprunte l’idée de DRV à la littérature SRAM et lui applique la conservation des données des cellules DFF. Une cellule DFF maître-esclave déclenchée par front positif peut être construite à partir de deux verrous D comme illustré à la Fig.3.2. Comme SRAM, les cellules DFF peuvent ne pas conserver les données lorsque la tension chute trop bas.

ÉVALUATION ET AMÉLIORATION DE LA SÉCURITÉ DES PUFS À ANNEAUX BISTABLES

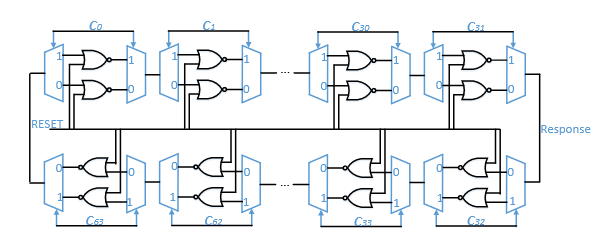

Figure 4.1: Schéma d’un seul BR-PUF à 64 étages

Comme le montre la figure 4.1, un PUF BR 64 bits est composé de 64 étages, où chaque étage a deux éléments de retard inverseurs (portes NOR à titre d’exemple). Un vecteur de défi C = {c1, c2 ,…, Cn } sélectionne les portes NOR utilisées dans chaque configuration d’anneau bistable en fournissant des valeurs aux portes MUX et DEMUX des étages. Étant donné que chaque porte NOR a une variation de processus unique, chaque vecteur de défi différent crée une configuration d’anneau bistable unique, et au total 224 différentes configurations peuvent être créées.

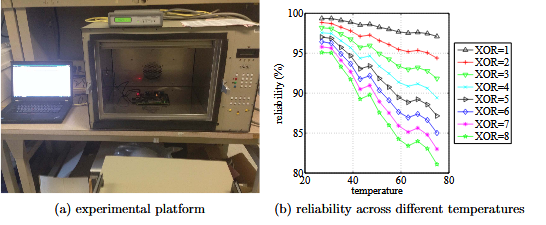

Figure 4.5: Évaluation de la fiabilité à différentes températures

Étant donné que la fiabilité de chaque BR PUF unique diminue avec la température, la fiabilité des résultats du BR PUF XOR se dégrade considérablement.

La fiabilité est le rapport des CRP cohérents lorsqu’un PUF fonctionne dans différentes conditions d’environnement telles que la température. Pour évaluer la fiabilité des PUF XOR BR, 8 BR PUF sont mesurés à différentes températures entre 270C et 750C, avec un 40Étape C, en utilisant une chambre environnementale Sun Electronics EC12 pour contrôler la température (Fig.4.5a). La fiabilité est évaluée en comparant les CRP collectés à 270C aux CRP collectés à d’autres températures.

UTILISATION DE MODÈLES STATISTIQUES POUR AMÉLIORER LA FIABILITÉ DES PUFS À RETARD

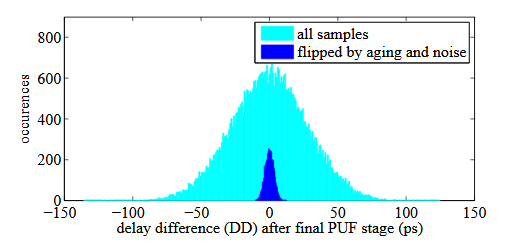

Figure 5.3: Différence de retard exacte DD de deux ensembles: 50 k échantillons d’or (colorés en cyan), le sous-ensemble d’échantillons retournés par le vieillissement et le bruit (colorés en bleu).

DDumin ≤ DD ≤ DDumax

Pour les données CRP d’Arbiter PUF, DDumax indique donc le DD maximum parmi les défis non fiables, et DDumin indique le DD minimum parmi les défis non fiables. Si seulement les vecteurs de défi satisfaisant à DD> DDumax ou DD

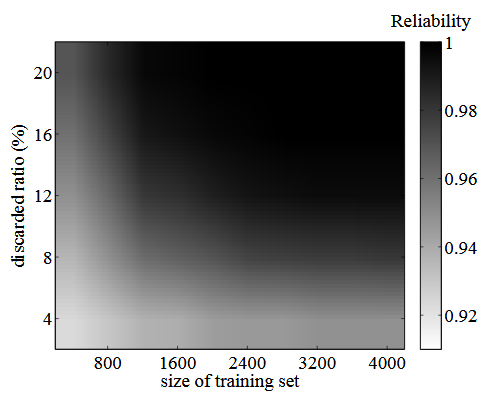

Figure 5.7: Validation sous vieillissement et bruit environnemental, sur toutes les instances de PUF simulées

Le compromis entre la taille de la formation et le ratio rejeté peut être vu sur la figure. Un dr plus grand est conservateur et peut compenser les prévisions de retard de qualité inférieure d’un modèle formé à partir d’un ensemble de formation plus petit.

Les défis qualifiés (DDmodèle 6∈[DD[DD[DD[DDmin, DDmax ]) sont appliqués sur les PUF, et leurs réponses sont comparées à la base de données dorée, le résultat est illustré à la Fig.5.7. Avec l’augmentation de la taille de la formation, les valeurs apprises pour DDmin et DDmax devenir plus précis, et moins de défis doivent être éliminés pour atteindre la même fiabilité. Le temps d’exécution pour entraîner le modèle SVM est modeste; lors de l’utilisation d’un ensemble d’entraînement de 4000 CRP, l’entraînement ne prend que 0,38 seconde.

PUF SÉQUENTIEL SANS HORLOGE À VOTE MAJORITAIRE AUTONOME

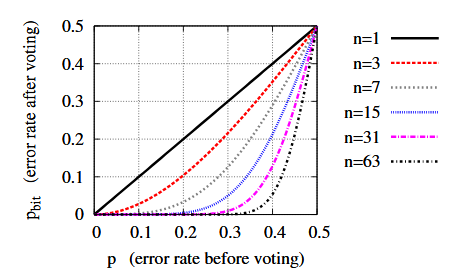

Figure 6.1: L’impact du vote majoritaire sur la fiabilité d’un seul bit

Pour toute probabilité p d’une erreur de sortie dans un seul essai, p bit est la probabilité correspondante d’avoir une erreur de sortie après avoir utilisé le vote majoritaire sur n essais. L’augmentation de n diminue la probabilité d’erreur, sauf pour les cellules avec p égal à 0,5.

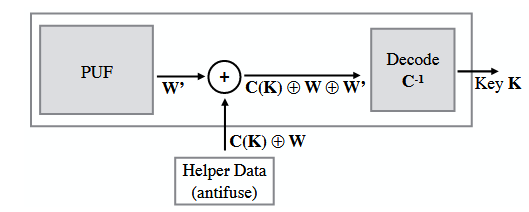

Figure 6.2: Génération de clé secrète basée sur PUF à l’aide de données d’assistance pour la correction d’erreur

Les données d’assistance sont générées au cours d’un processus d’inscription unique et sont fixées sur la durée de vie du PUF.

Les améliorations de fiabilité telles que le vote majoritaire complètent l’utilisation de la correction d’erreurs. Un exemple de correction d’erreur utilisant la construction à décalage de code est illustré à la Fig.6.2. Une clé secrète arbitraire K est choisie pour chaque PUF lors de l’inscription puis codée en un mot de code C (K) qui est XOR avec la réponse PUF W pour générer des données d’assistance.

CONCLUSIONS

Sous l’impulsion de la loi de Moore, l’industrie des semi-conducteurs a connu une mise à l’échelle physique continue au cours des dernières décennies. Cette avancée facilite grandement le développement d’appareils électroniques comme les téléphones intelligents, les tablettes, mais propose également de nouveaux défis pour les chercheurs en sécurité matérielle. Cette thèse présente certains de nos travaux récents dans l’avancement du calcul CMOS sécurisé avec des fonctions intrinsèques: c’est-à-dire les fonctions physiques non clonables (PUF). Trois sujets sont étudiés: les variations de processus à l’échelle nanométrique, la modélisation basée sur l’apprentissage automatique et la sensibilité au bruit.

Le chapitre 1 de cette thèse énumère le défi et les opportunités dans la conception de circuits cryptographiques nanométriques. Nous prédisons que, bien que les variations de processus soient préjudiciables à la conception de circuits conventionnels, les PUF ont été proposés comme solution viable pour exploiter la nature imprévisible des variations de processus pour les applications de sécurité. Des terminologies comme les paires défi-réponse (CRP), la fiabilité, l’unicité et l’uniformité sont définies dans ce chapitre.

Étant donné que les PUF exploitent les variations microscopiques du processus, ils sont donc sensibles au bruit ambiant, comme de légères variations de température ou de tension d’alimentation. En raison de cette sensibilité, un PUF peut ne pas produire de réponse cohérente pour le même défi dans différentes conditions environnementales. Pour répondre à la fiabilité des primitives PUF actuellement proposées, deux mécanismes PUF très fiables sur deux architectures de mémoire communes, SRAM et D Flip-flop sont proposés dans les chapitres 2 et 3. Pour améliorer l’efficacité de nos mécanismes PUF proposés, nous avons combiné un algorithme comme recherche binaire, méthode avancée de Machine Learning comme Artificial Neural Network (ANN) dans ces deux ouvrages.

Source: Université du Massachusetts

Auteur: Xiaolin Xu